Foram encontradas 20 questões.

Um amplificador operacional apresenta rejeição de modo comum por ser um amplificador do tipo:

Provas

Questão presente nas seguintes provas

O filtro digital, caracterizado por uma resposta ao impulso que se anula após um tempo finito e que, por não possuir realimentação, não acumula erros, é do tipo:

Provas

Questão presente nas seguintes provas

1299914

Ano: 2009

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UERJ-SGP

Orgão: UERJ

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UERJ-SGP

Orgão: UERJ

Provas:

Ao longo da evolução dos microcomputadores IBM-PC, diferentes tipos de fonte de alimentação foram surgindo, os quais se tornaram de fato “padrões industriais” no mercado. De um padrão para outro, foram mudando os formatos, o número de pinos, as tensões e os sinais da fonte de alimentação.

O tipo de fonte de alimentação para microcomputadores IBM-PC, que fornece tensões de 0 V,+ 5V, -5V, +12V, -12V, + 3,3V (opcional) e os chamados sinais Soft Power, que permitem o desligamento da fonte por software (normalmente pelo sistema operacional, ao realizar-se shut down), é do padrão:

Provas

Questão presente nas seguintes provas

O esquema abaixo representa um circuito básico de eletrônica digital denominado:

Provas

Questão presente nas seguintes provas

Na arquitetura de protocolo TCP/IP, o protocolo UDP é da camada de:

Provas

Questão presente nas seguintes provas

A tecnologia Ethernet é predominante em ambientes de redes na atualidade. Os dados trafegam pela rede encapsulados em um frame padronizado, que possui campos de cabeçalho bem definidos. O conteúdo do campo de preâmbulo de um frame Ethernet estabelece:

Provas

Questão presente nas seguintes provas

A linguagem de descrição de hardware VHDL permite descrever sistemas digitais com o propósito de síntese ou de simulação. O código VHDL abaixo descreve um registro. Leia e interprete o código.

reg: process(Rst,Clk)

begin

if Rst = ‘1’ then

Qreg <= ”00000000”;

elsif (Clk=’1’and Clk’event) then

if (Load=’1’) then

Qreg <= Data;

else

Qreg <= Qreg(1 to 7) & Qreg(0);

end if;

end if;

end process;

Além da operação reset, o registro descrito pelo código pode receber:

Provas

Questão presente nas seguintes provas

Um flip-flop tipo D copia o estado presente na entrada de dados (D) quando a entrada de clock (Ck) recebe a transição de ativação de comando.

O tempo mínimo em que um nível deve permanecer estável na entrada D, logo após o instante em que ocorre, na entrada Ck, uma transição de ativação de comando do flip-flop, é denominado de:

Provas

Questão presente nas seguintes provas

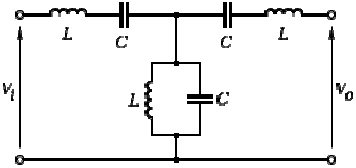

Observe o circuito abaixo:

Esse circuito é classificado como um filtro do tipo:

Provas

Questão presente nas seguintes provas

As três regiões de operação de um MOSFET são:

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container