Foram encontradas 20.587 questões.

A respeito do processo de conversão analógico digital e da PCM (modulação por pulsos codificados), julgue o item seguinte.

As leis de compansão (companding), conforme recomendação da União Internacional de Telecomunicações, têm por objetivo gerar um sinal na saída do compressor cuja função densidade de probabilidade dos valores de amplitude é aproximadamente uniforme dentro da faixa dinâmica do quantizador.

Provas

Questão presente nas seguintes provas

A respeito do processo de conversão analógico digital e da PCM (modulação por pulsos codificados), julgue o item seguinte.

Nas formas de compansão (companding) por Lei A e Lei μ definidas pelo padrão ITU-T G.711, a Lei μ tem ruído de quantização pouco maior que a Lei A, uma vez que a palavra zero não é utilizada, o que aumenta a faixa dinâmica do quantizador.

Provas

Questão presente nas seguintes provas

A respeito do processo de conversão analógico digital e da PCM (modulação por pulsos codificados), julgue o item seguinte.

Na multiplexação por divisão do tempo (TDM – time division multiplexing) de sinais telefônicos digitais, o primeiro nível da hierarquia norte-americana é composto por trinta tributários do tipo DS0, gerando um sinal multiplexado de 1,544 Mbps.

Provas

Questão presente nas seguintes provas

A respeito do processo de conversão analógico digital e da PCM (modulação por pulsos codificados), julgue o item seguinte.

Em enlaces digitais entre países que utilizem diferentes leis de compansão (companding), deve prevalecer a utilização de Lei A, sendo necessária a conversão da representação de Lei μ para a Lei A em países que utilizem a Lei μ.

Provas

Questão presente nas seguintes provas

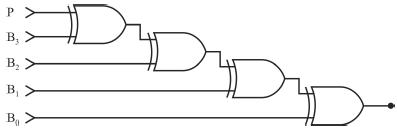

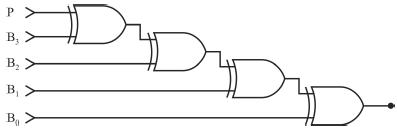

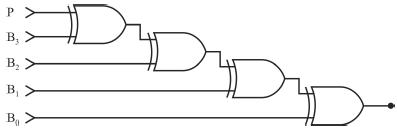

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Se dois bites forem invertidos, a saída do verificador de paridade não indicará qualquer erro.

Provas

Questão presente nas seguintes provas

Julgue o item a seguir, referente a amplificadores.

Em um amplificador operacional ideal, caso as entradas sejam idênticas, a saída será zero.

Provas

Questão presente nas seguintes provas

Julgue o item a seguir, referente a amplificadores.

Em um amplificador operacional real, a tensão de offset de entrada é diferente de zero.

Provas

Questão presente nas seguintes provas

Julgue o item a seguir, referente a amplificadores.

Um amplificador na configuração cascode possui um estágio emissor comum seguido por um estágio base comum.

Provas

Questão presente nas seguintes provas

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Quando o identificador de paridade identificar um erro, sua saída irá para o nível alto.

Provas

Questão presente nas seguintes provas

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Em caso de erro, o verificador de paridade apresentado não conseguirá identificar qual bite estará errado.

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container