Foram encontradas 50 questões.

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: DECEA

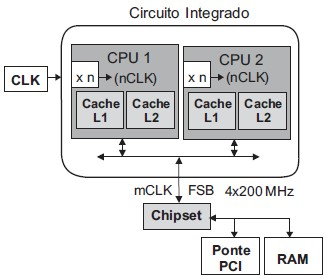

A figura abaixo mostra a arquitetura de um computador com processador dual core.

A respeito desta arquitetura, é INCORRETO afirmar que

Provas

- Gerenciamento de MemóriaAlgoritmos de Substituição de Páginas

- Gerenciamento de MemóriaFalha de Página (Page Fault)

- Gerenciamento de MemóriaMemória Virtual (Conceito)

- Gerenciamento de Processos

Considerando que um sistema operacional implementa o recurso de memória virtual, analise as afirmativas a seguir.

I – Quando o processador encontra uma instrução ausente na memória RAM, este gera internamente uma exceção do tipo armadilha.

II – Cabe ao aplicativo implementar o manipulador de exceção que comuta as páginas entre memória RAM e memória virtual.

III – Geralmente, o algoritmo usado para a comutação de páginas é o LRU (Least Recently Used).

É(São) correta(s), APENAS, a(s) afirmativa(s)

Provas

entity CONTADOR is

port (CLK, EN, CLR, LOAD, UP: in std_logic;

D: in std_logic_vector (3 downto 0);

Q: out std_logic_vector (3 downto 0));

end CONTADOR;

architecture comportamento of CONTADOR is

signal CONT: std_logic_vector (3 downto 0);

begin

process (CLK)

begin

— — linha L1

if (CLK’event and CLK = ‘1’) then

— — linha L2

if (LOAD = ‘1’) then CONT <= D;

— — linha L3

elsif (EN = ‘1’ and UP = ‘1’) then

CONT <= CONT + “0001”;

elsif (EN = ‘1’ and UP = ‘0’) then

CONT <= CONT - “0001”;

end if;

end if;

end process;

Q <= CONT;

end comportamento;

A arquitetura implementada refere-se a um contador crescente ou decrescente com clear síncrono. No código em VHDL, a linha

if (CLR = ‘1’) then CONT <= “0000”; end if;

deve ser inserida no lugar da linha

Provas

Um programador dispõe de uma matriz H quadrada, de dimensão N par, contendo números reais, de acordo com

\( H=\begin{bmatrix} h_{11}&h_{12}&...&h_{1N}\\h_{21}&h_{22}&...&h_{2N}\\\vdots&\vdots&...&\vdots\\h_{N1}&h_{N2}&...&h_{NN}\end{bmatrix} \)

Deseja-se reordenar esses números na matriz H, utilizando apenas uma variável real P. O novo conteúdo da matriz H deverá ser

\( H=\begin{bmatrix} h_{NN}&h_{N(N-1)}&...&h_{N1}\\h_{(N-1)N}&h_{(N-1)(N-1)}&...&h_{(N-1)1}\\\vdots&\vdots&...&\vdots\\h_{1N}&h_{1(N-1)}&...&h_{11}\end{bmatrix} \)

Para isso, o programador escreveu em pseudocódigo o seguinte algoritmo:

Para I de 1 até (N/2)

Para J de 1 até N

![]()

Fim do para

Fim do para

As linhas do algoritmo que estão faltando são:

Provas

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

A tabela verdade de uma função lógica é mostrada acima, onde X e Y são variáveis lógica de entrada, e Z é a variável de saída. Deseja-se reproduzir essa função em um controlador lógico programável (CLP). O diagrama LADDER que possui a mesma tabela verdade é

Provas

- Modelo TCP/IPIntrodução ao Modelo TCP/IP

- Modelo TCP/IPModelo TCP/IP: Camada de Rede

- Modelo TCP/IPModelo TCP/IP: Camada de Transporte

- Modelo TCP/IPModelo TCP/IP: Camada de Aplicação

Considere as afirmativas a seguir, sobre a arquitetura TCP/IP, que é, atualmente, a que tem maior utilização nas redes de dados.

I – O Internet Protocol (IP), um dos principais protocolos em uma rede TCP/IP, é responsável pelo transporte de datagramas entre a máquina de origem e a máquina de destino, utilizando os endereços lógicos para determinar o melhor caminho, sendo cada datagrama independente dos demais trafegando na rede, não havendo necessidade de estabelecer conexão para o envio de informações.

II – A camada de transporte tem como uma de suas responsabilidades rotear, com confiabilidade, os dados entre a máquina de origem e a máquina de destino, quando é utilizada uma arquitetura cliente servidor.

III – A camada de aplicação é responsável por oferecer os serviços de rede aos usuários, como por exemplo, Web, correio eletrônico, acesso remoto entre outros.

É(São) correta(s), APENAS, a(s) afirmativa(s)

Provas

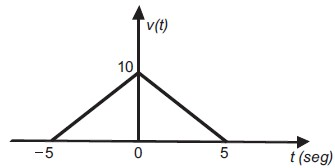

Aplicando-se a segunda derivada \( (v"(t)=\dfrac{d^2v}{dt^2}) \) no pulso triangular mostrado na figura acima, resulta na seguinte sequência de impulsos \( \delta \) (t), deslocados no tempo:

Provas

Um sinal de áudio no padrão WAV é gerado com uma frequência de amostragem de 40.000 amostras/s (valor que foi aproximado para facilitar o cálculo) e digitalizado com 16 bits/amostra. Uma música, que tenha duração de 3,5 minutos, ao ser digitalizada, ocupará um espaço em memória, em Mbytes, de

Provas

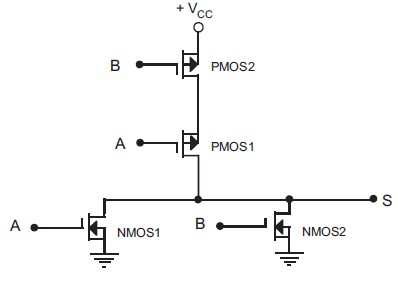

Com relação ao circuito da figura acima, considere as afirmativas a seguir.

I – Para a saída S ser ativada, é necessário que PMOS1 e PMOS2 conduzam simultaneamente.

II – Para que a saída S seja igual a 0, basta conduzir um dos transistores NMOS.

III – Para que a saída S seja ativada, é estritamente necessário que ambas as entradas A e B sejam iguais a 1.

É(São) correta(s), APENAS, a(s) afirmativa(s)

Provas

mov dx,0601h

in al,dx

out dx,eax

Considere o código em assembler, mostrado acima, usado por um processador de pelo menos 32 bits de dados da família x86. Os números de ciclos de barramento provocados pelas instruções in e out, num barramento periférico de 16 bits de dados, respectivamente, são:

Provas

Caderno Container