Foram encontradas 12.749 questões.

1394544

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Considere as proposições abaixo a respeito da memória cachê.

I – No evento cache miss, cada erro da cache faz com que a memória principal precise ser acessada. Se a quantidade de erros for muito grande, o desempenho do equipamento ficará comprometido.

II – No processo de escrita na memória do tipo write trough, a informação é escrita antes na memória cache e depois na memória principal, independente se a página for ou não utilizada.

III – No processo de escrita na memória do tipo write back, a informação é escrita somente na memória cache, sendo a memória principal atualizada somente quando a página não for mais utilizada.

IV – No processo de escrita na memória do tipo write forward, ocorre na memória cache e na memória principal, somente quando a página não for mais utilizada.

Estão corretas APENAS as afirmativas:

Provas

Questão presente nas seguintes provas

1393869

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Convertendo-se a versão binária de 16 bits em complemento a 2 do número (-22)10 para números binários com 32 bits obtémse

Provas

Questão presente nas seguintes provas

1393760

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Considere uma máquina com memória endereçada byte a byte, com tamanho de 216 bytes e tamanho de bloco de 8 bytes. Suponha que seja utilizada uma memória cache com mapeamento direto, composta de 32 linhas. Considere, ainda, o seguinte endereço de memória: 0001 0001 0001 1011. Em qual linha da cache deve ser armazenado o byte com este endereço?

Provas

Questão presente nas seguintes provas

1393641

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

A tabela a seguir mostra informações de cinco jobs.

| A | B | C | D | E | |

| Tempo de execução | 220 | 150 | 80 | 200 | 50 |

| Tempo de chegada | 0 | 0 | 3 | 3 | 4 |

Sabendo-se que o escalonador utiliza o algoritmo de job mais curto primeiro (SJF), pergunta-se qual a diferença entre o tempo médio de resposta e o tempo médio de resposta ótimo para os cinco jobs.

A diferença é

Provas

Questão presente nas seguintes provas

1393388

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Julgue as afirmações a seguir e marque a alternativa correta correspondente.

I) O DMA (Acesso Direto à Memória) é uma técnica que libera a CPU das operações de E/S de baixo nível. Em controladoras com suporte à DMA, a transferência de dados é feita diretamente entre o buffer do dispositivo e a memória, sob a responsabilidade da controladora do dispositivo.

II) A intercalação (interleaving) é uma técnica utilizada pela controladora do dispositivo para que ela tenha tempo de transferir os dados entre o buffer do dispositivo e a memória.

III) Uma das maneiras de se evitar a ocorrência de impasses é permitir que processos que estão mantendo recursos previamente alocados possam solicitar novos recursos, tendo assim condição de terminar sua execução.

Provas

Questão presente nas seguintes provas

1392705

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

A memória ROM presente na placa-mãe de um microcomputador guarda um programa chamado SETUP. Através do SETUP, podem-se alterar configurações do computador como sequência de boot e detecção de HDs. O SETUP guarda os dados desta configuração em uma memória

Provas

Questão presente nas seguintes provas

1389824

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

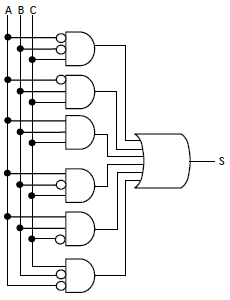

Observe o circuito combinacional abaixo:

Em termos de funcionalidade lógica, o circuito é equivalente a

Provas

Questão presente nas seguintes provas

1388020

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

O resultado, em base decimal, de A XOR B, onde A = (24)16 e B = A + (14)16 é

Provas

Questão presente nas seguintes provas

1384277

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FUNRIO

Orgão: CEITEC

Os aperfeiçoamentos tecnológicos nos computadores não têm se limitado aos processadores, embora, de certa forma, sejam mais rápidos e profundos nestes. Um exemplo de modificação que levou, inclusive, alguns periféricos a perderem compatibilidade com equipamentos mais antigos, é o barramento de comunicação com os discos rígidos.

Marque a opção que apresenta os padrões de interface de barramento para conexão de discos rígidos utilizados nos computadores atuais.

Provas

Questão presente nas seguintes provas

1383743

Ano: 2012

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: COREN-RN

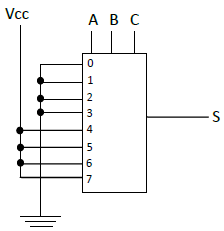

Um multiplexador é um circuito combinacional capaz de gerar funções lógicas. A figura abaixo mostra uma função lógica de 3 variáveis implementada com um multiplexador.

Considerando que a entrada 0 será selecionada quando A=B=C=0, a entrada 1 será selecionada quando A=B=0 e C=1, e assim sucessivamente, a função lógica simplificada realizada por este circuito combinacional é

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container