Foram encontradas 120 questões.

O flip-flop gatilhado por borda de descida, assim como o flipflop JK, apresenta uma metade denominada servidor e uma denominada mestre, que permanece transparente à entrada enquanto o sinal de clock tiver valor lógico 1.

Provas

Considere que, em um flip-flop tipo JK gatilhado por borda de descida, a saída Q atual tenha o valor lógico 1 e as entradas J e K tenham ambas o valor lógico 1. Nesse caso, após a ocorrência de uma borda de descida no clock, a saída Q permanecerá no valor lógico 1.

Provas

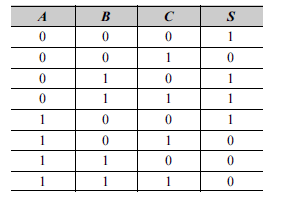

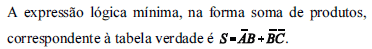

A tabela acima corresponde à tabela verdade de um circuito lógico, sendo que as entradas são as variáveis A, B e C, e a saída, a variável S. Com relação a essa tabela, julgue os itens que se seguem.

O mapa de Karnaugh é útil no processo de obtenção da expressão mínima na forma soma de produtos, mas não, na obtenção da forma mínima produto de somas.

Provas

A tabela acima corresponde à tabela verdade de um circuito lógico, sendo que as entradas são as variáveis A, B e C, e a saída, a variável S. Com relação a essa tabela, julgue os itens que se seguem.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

O circuito representado na figura apresentará maior velocidade de comutação se for implementado com portas lógicas CMOS, do que se implementado com portas ECL.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

Os símbolos usados na figura indicam que as portas lógicas utilizadas são do tipo coletor aberto.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

É possível implementar um circuito que realize uma função lógica equivalente à realizada com o circuito mostrado, usando-se apenas portas NÃO-OU com números de entradas convenientes.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

Se a entrada E assumir o valor lógico 1, então, independentemente do valor lógico das demais entradas, o valor lógico da saída x será 0.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

Se os valores lógicos das entradas A, B, C, D e E forem, respectivamente, 0, 1, 0, 1 e 0, então, a saída x assumirá o valor lógico 1.

Provas

Com relação ao circuito combinacional mostrado na figura acima, julgue os seguintes itens.

Na figura, a porta lógica indicada por V corresponde a uma porta E.

Provas

Caderno Container