Foram encontradas 60 questões.

Determine VR3 para o circuito abaixo, considerando os diodos de silício. Utilizar o modelo equivalente simplificado, em que VD=0,7V, RD=desconsiderado.

Provas

Determine ID2 para o circuito abaixo, considerando os diodos de silício. Utilizar o modelo equivalente simplificado, em que VD=0,7V, RD=desconsiderado.

Provas

Supondo o amplificador operacional ideal na figura abaixo, calcule a tensão nos terminais VO e assinale a alternativa que apresenta o valor correto. Todos os resistores estão representados em Ohms [Ω].

Provas

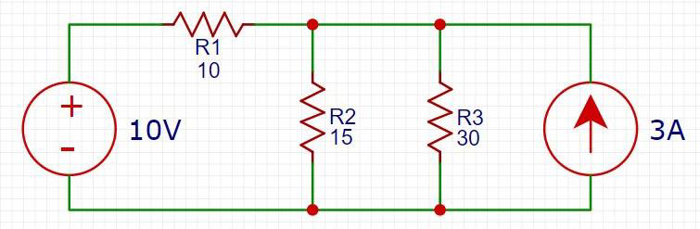

Assinale a alternativa que apresenta os valores corretos de tensão e corrente no resistor R2. Todos os resistores estão representados em Ohms [Ω].

Provas

Considerando Flip-Flops JK, em que o estado atual Q2Q1Q0 = 111 e com disparo apenas na borda de descida do clock, qual a sequência que este circuito Q2Q1Q0 executa com os pulsos de clock?

Provas

Considerando Flip-flops JK, em que o estado atual Q1Q2=01 (Q1=0 e Q2=1) e com disparo apenas na borda de descida do clock, qual a sequência que este circuito executa com os pulsos de clock?

Provas

Determine a expressão que representa a tabela verdade abaixo:

A | B | C | S |

0 | 0 | 0 | 1 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 1 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 0 |

1 | 1 | 1 | 0 |

Provas

Considerando um Flip-flops JK, em que o estado inicial de Q=0 e com disparo apenas na borda de descida do clock, qual o estado de saída Q após 3, 5, 7 e 8 pulsos de clock, respectivamente?

Provas

Considerando Flip-flops JK, em que o estado atual de Q1=1, Q2=0 e Q3=1 e com disparo apenas na borda de descida do clock, qual o estado de saída Q1, Q2 e Q3 após 4 pulsos de clock?

Provas

Determine a expressão que representa a tabela verdade abaixo:

A | B | S |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Provas

Caderno Container